业务咨询,可拨打13500040761,或电邮至george qiu@basicae.com,或扫描文末微信二维码与我们联系!

Tessent是Mentor Graphics(现在Siemens)推出的针对设计各个方面进行完备测试的解决方案,以确保实现高质量的产品和成本控制。

主要特性:

l提供贯穿产品生命周期的完整测试,从晶圆、封装测试、老化、在系统和现场测试。

l对测试压缩、内建逻辑自测试、内建存储器自测试以及边界扫描拥有一流的解决方案。

l使用物理版图数据来改善测试和良率分析。

l紧密整合测试和良率分析解决方案。

逻辑测试

先进设计技术使用的同时也给SoC逻辑部分要达到高质量的测试带来了明显的挑战。为了应对这些挑战,Siemens EDA公司提供了业界强大的逻辑测试解决方案:Tessent Scan(DFTAdvisor)、Tessent TestKompress、Tessent LogicBIST以及Tessent Fastscan. 这些解决方案已经存在超过十年以上,有数以千计的设计成功流片,以及成功使用压缩和更少向量方法的高质量测试案例。同时,它们提供较大的灵活性以达到测试时间与测试质量的有效优化。

Tessent Scan (DFTAdvisor)测试综合

Tessent Scan (DFTAdvisor) 测试综合工具自动插入测试结构电路,支持全扫描或部分扫描的测试逻辑,能够自动识别电路中的时序单元并自动转换成可扫描的单元,并能够把电路中可扫描的单元串接成扫描链,从而大大增强了IC和ASIC设计的可测试性。此外,利用它在设计过程的早期阶段进行可测性分析,在测试综合生成和测试向量自动生成之前发现并修改违反测试设计规则的问题,尽可能提高ATPG的效率并缩短测试开发的周期。 下图则显示了利用工具进行Wrapper Chain的插入情况。

Tessent FastScan自动测试向量生成(ATPG)

Tessent FastScan为全扫描IC设计或规整的部分扫描设计生成高质量的测试向量。Tessent FastScan支持所有主要的故障类型,它不仅可以对常用的Stuck-at模型生成测试向量,还可以针对关键时序路径、transition模型生成at-speed测试向量、针对IDDQ模型生成IDDQ测试向量、针对纳米级工艺的桥接故障生成Bridge测试向量。此外Tessent FastScan还可以利用生成的测试向量进行故障仿真和测试覆盖率计算。

Tessent TestKompress提供嵌入式压缩引擎的ATPG生成

Tessent TestKompress基于拥有的EDT测试技术,能够提供极为有效的测试向量压缩。在不损失任何测试覆盖率的情况下,Tessent TestKompress可以达到100倍的测试时间与测试向量大小的压缩。对于ATE来说,这些经过压缩的测试向量仍然与未压缩向量的工作方式完全相同,然而对于测试仪存储器的占有量却大幅减少,同时获得了更快的测试时间。通过Tessent TestKompress产生的测试向量,可以保存为WGL、STIL等多种格式。

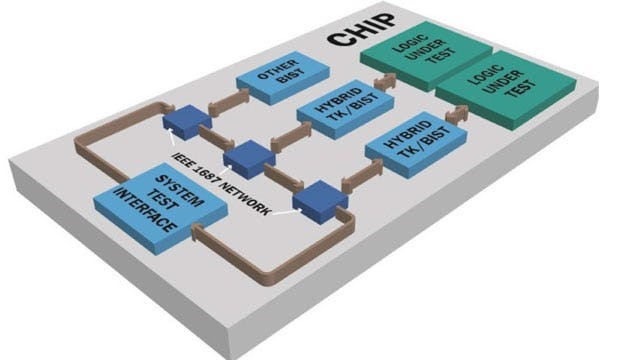

Tessent LogicBIST 安全关键应用的芯片测试

Tessent™ LogicBIST 是适合安全关键设备 (如汽车和医疗应用中使用的IC)的高质量芯片测试解决方案。Tessent LogicBIST 具有可提高LBIST测试覆盖率并大幅减少图形数目的先进技术,是目前可获取的最高效的系统内测试解决方案。

Tessent BoundaryScan 全面的边界扫描及I/O测试解决方案

Tessent BoundaryScan支持标准的1149.1边界扫描单元、1149.1定制边界扫描单元以及可选的用于驱动交流耦合差分I/O单元的1149.6边界扫描单元。同时针对非接触式I/O测试也提供了独特的基于1149.1标准的解决方案。

Tessent MemoryBIST 内嵌存储器测试

Tessent MemoryBIST是目前业界应用最广的存储器测试生成工具,可以灵活地在ASIC或IC中自动实现内嵌存储器阵列的RTL级BIST结构。Tessent MemoryBIST支持多种测试算法,并支持用户自定义的测试算法。可以对一个或多个内嵌存储器自动创建BIST逻辑,完成BIST逻辑与存储器的连接,它能够在多个存储器之间共享BIST控制器,实现并行测试,从而显著缩短测试时间和节约芯片面积。另外,它的BIST结构中还包括故障的自动诊断功能,方便了故障定位和开发针对性的测试向量。

混合信号测试

Tessent混合信号解决方案为PLL,DLL和multi-Gb/s SerDes提供了完整的、参数化的嵌入式测试提供了完善的技术手段。该解决方案可以测量波形、多种类型的抖动以及其它重要的性能参数。该解决方案基于无限时间分辨率分析(ULTRA)技术,此技术能帮助许多用户设计工作在超过10GHz的频率之上。

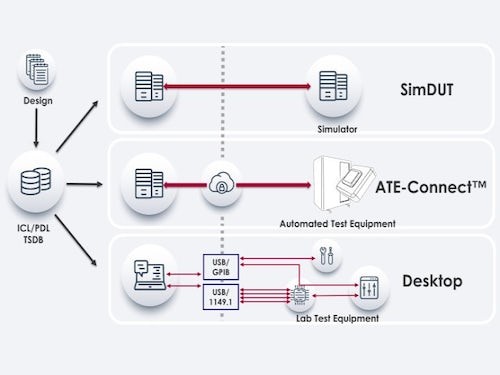

Tessent SiliconInsight交互环境

随着设计越来越复杂,缩短芯片提交阶段的时间关键在于把芯片交付到客户手中。理解在什么样的情况下芯片失效以及有效隔离问题,将帮助设计、测试和DFT工程师加速调试和特性分析方法的时间。Tessent SiliconInsight解决方案提供了一个自动化的交互环境,用于测试提交、调试和包含Tessent BIST能力的器件的硅片特性分析方法。Tessent SiliconInsight大大增加了芯片设计者和测试工程师在芯片测试、调试以及快速上市的生产力。

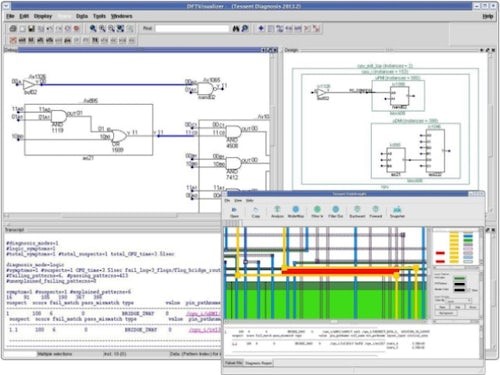

Tessent YieldInsight & Tessent Diagnosis诊断驱动的良率分析

在一个新产品的改进当中,可能需要花费几周甚至几个月来确认导致低良率的根源。Tessent YieldInsight提供了先进的统计分析和数据挖掘技术来补充Tessent Diagnosis的自动化诊断能力。利用生产制造测试结果和设计数据,该方案帮助IC制造者可以在物理失效分析前识别造成所有规则缺陷的可能原因。该工具显著缩短了发现良率低下根源的时间,同时能识别更多其它本身无法侦测的良率限制因素。

更多业务咨询,可扫描下方二维码添加微信,或拨打电话13500040761,或电邮george qiu@basicae.com与我们联系!