接上文:三维芯片封装热协同设计完整指南 - 10点重要考虑(1)

整合 Simcenter Flotherm 的 Calibre温度感知设计流程

6. 在布图规划之前,反馈温度信息

在 IC 设计流程开始之前,为 IC 设计团队提供有关芯片平均温度和每个芯片温度变化的信息,可以极大地帮助进行布图规划 [参考文献 1]。布图规划对设计质量至关重要,因为在布图规划期间做出的决策可以缓解或加剧这种温度变化。就像封装预选活动一样,前期 IC 设计旨在探索设计空间,以便提出将热影响考虑在内的最佳解决方案,因此必须快速评估许多想法。

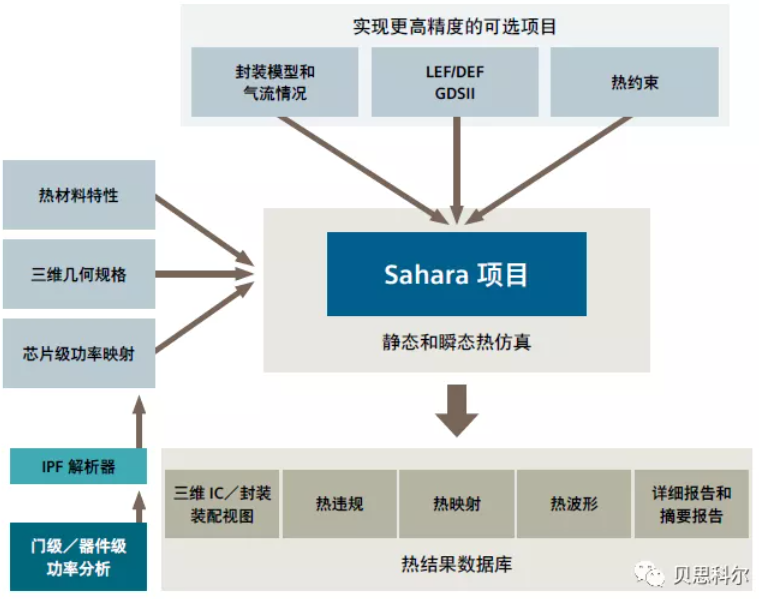

现在可以快速迭代不同布图规划的热影响,这些布图规划同时将封装的热设计直接整合到 IC 设计流程中,因为Simcenter Flotherm 现在可以与 Simcenter 的 Calibre 套件(DESIGNrev 和 RVE)一起用来仿真 Calibre 内置封装的热模型,提供具有完全温度感知能力的 IC 设计流程,其代号为 Sahara 项目。

Sahara 项目专注于从前期设计探索到最终 sign-off 的全流程。Sahara 项目可以创建 3DIC 的 SimcenterFlotherm 模型,使得 3DIC 封装能够导入到更大的电路板级或系统级模型中,从而充分考虑应用环境的影响。

7. 在布图规划期间使用功能块功率预算

一旦开始进行布图规划,您需要从 IC 设计团队处拿到高层次的功率映射,导入到封装的热模型中。Simcenter Flotherm 拥有的 Die SmartPart 可以读入 CSV文件格式的功率,从而自动完成并迅速反馈结果,因为仿真模型往往只需要运行短短的几分钟,就可指明 TSV在哪里引入可改善散热性能或哪里需要其他设计变更。例如,对于确保两个或更多个不同功能块在非常相似的温度下运行以消除定时问题,它可能会非常重要。

8. 探索硅通孔布局

对于逻辑搭载逻辑的 3DIC,这应该在不同芯片之间隔开设计时,和在芯片间和芯片内布图规划期间(要求每个芯片的功率映射)加以考虑。

在此阶段,有机会在保持功能块相对位置不变的情况下,将其沿 x 和 y 方向(xy 扩展)移动,只是调整它们之间的间距(空白空间)使得能够插入 TSV 以检查它们对芯片热点的影响。在知道与芯片厚度成比例关系的 TSV 尺寸和间距后,具有更高的贯通面热导率的块可以叠加到Simcenter Flotherm 中的这些空白区域的芯片厚度上,以局部覆盖硅的属性。

在布图规划期间优化功能块和 TSV 布局将是 IC 设计流程的一部分,而热设计只是该过程的约束条件之一。

9.使 IC 设计流程感知温度

随着布图规划的推进,在进一步细化设计时,热设计工作需要把重点放在芯片之间的热相互作用的细节上。芯片的功率映射变得更加详细,并且在 3DIC 的情况下,作为电气设计的一部分,需要定义 TSV 的数量和位置。时钟树综合 (CTS) 是 IC 设计流程中的关键步骤,必须等到它完成后,芯片才能布线;物理时序收敛要考虑布局、时钟树综合和布线,这些都必须具有时序感知能力才能让现代同步 IC 设计实现时序收敛。Siemens 公司与 TSMC 携手创建基于 Simcenter FloTHERM和 Calibre DESIGNrev 与 RVE 的热分析流程,是一个观察环境的工业标准的物理验证结果 [参考文献 3]。

图 3:TSMC 参考流程协作。

Sahara 项目对于获得时序收敛和 sign-off 同时有热感知能力的设计所需的精细具体工作至关重要。它提供了简单易用、快速准确的工具,通过内置于该解决方案的自动网格化功能,在关键的模型区域(如芯片)使用局域化网格的方式实现对完整封装模型内 3DIC 的芯片和中介层的热仿真。

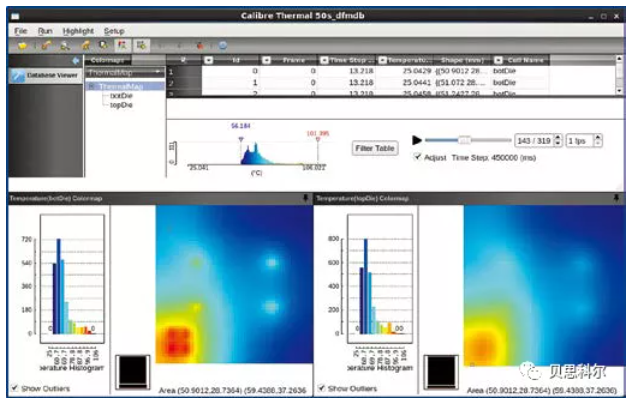

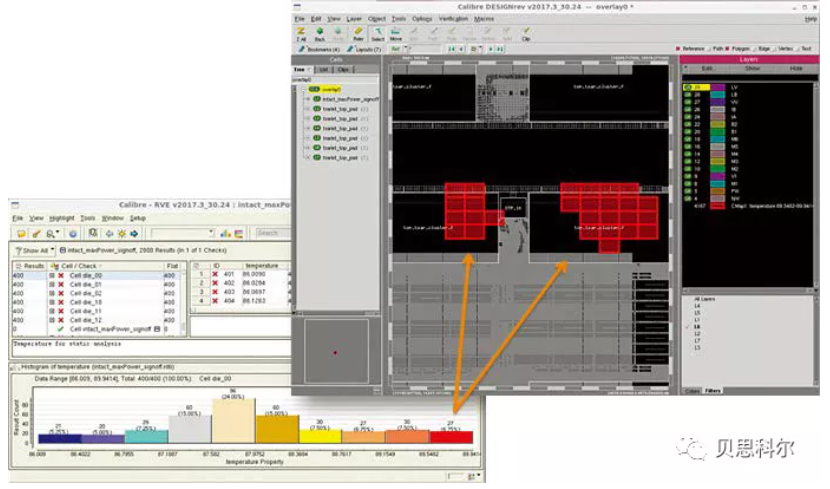

图 4:Caliber DESIGNrev 中的热模型的装配视图。

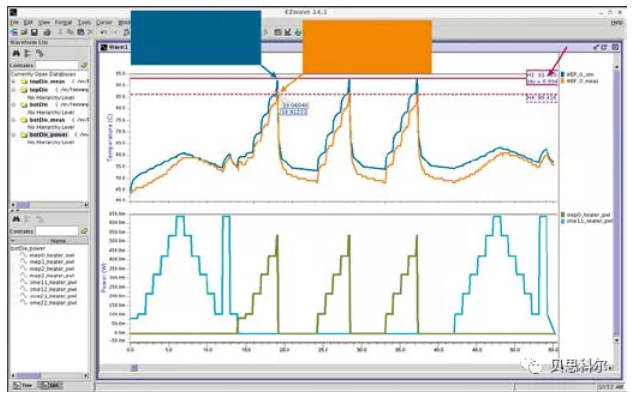

此解决方案利用能够由功率分析工具生成的芯片功率映射文件创建热量分布图,以用于散热设计和进行散热的约束违规检查。热结果还可以在 Calibre RVE 中以直方图形式显示,并且在 Calibre DESIGNrev 中,热点会在设计中突出显示。在瞬态分析中,可以使用高容量、高性能的图形化波形环境 Simcenter EZwave 显示温度与时间的关系图。功率和温度波形可以显示在同一窗口上,甚至可以叠加以便轻松获得相关性。

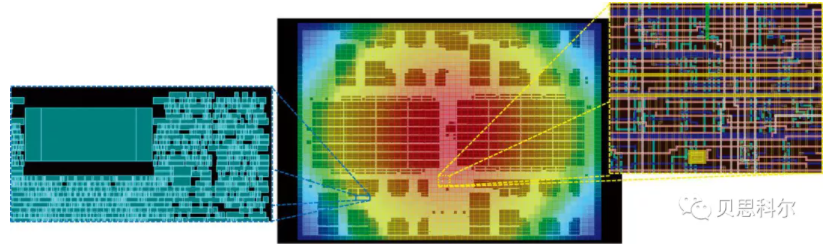

图 5:Sahara 项目的热建模方法。

在此流程中,热模型的生成和验证,基于 GDSII 的热特性提取,以及基于实例功率文件 (IPF) 的功率映射生成,均是在 Calibre 环境中完成。因此,考虑到金属化,例如互连和芯片内的 TSV,芯片的热模型比在 IC 设计流程之外通常能构建的模型更精确。

图 6:Sahara 项目中的热彩色图和直方图。

图 7:Calibre RVE 中的热直方图和 Calibre DESIGNrev 中的热点覆盖。

图 8:利用 Simcenter EZwave 显示的温度和功率与时间的关系曲线。

时序收敛和 sign-off

10.使用精确的芯片级热分析

当执行完整的芯片—封装—系统热仿真时,通过从布局中提取来自动计算各向异性等效热特性,可以解决细粒度细节问题。随着重心转向获得时序收敛和 signoff,提取的粒度可以增加。

图 9:高效热特性提取 (EFFP) 可降低模型复杂度并加速仿真(图片由 CEA-Leti提供)。

IPF 支持允许使用门级和器件级功率分析来构建所需的细粒度功率图,以便精确捕获芯片上的热点。在实例数量非常多(源实例达数百万)的设计中自动压缩电源,可以加速 Simcenter Flotherm 仿真。

图 10 显示了使用 EFFP 和有 9 个金属化层的非常复杂的BEOL 简化之后,一个拥有超过 150,000 个细粒度结构(包括 TSV 和 μ-凸块)的器件可能达到的细节水平。

最后,自动约束检查可以避免容易出错且耗时的热约束手动验证。对于图 10 所示设计,EFFP 和智能功率映射转换功能将仿真时间从数小时/数天缩短到不到一小时:

• 热特性提取 (EFFP):30 分钟(每个热模型一次)

• 从 IPF 生成功率映射:不到 2 分钟(每个应用场景一次)

• 完整封装三维 IC 的热仿真:50 分钟

图 10:详细的 sign-off 热分析(图片由 CEA-Leti 提供)。

结语

在先进技术和现代应用中,主要是高级三维 IC 中,以封装为中心的方法不再有效。集成 Sahara 项目的Simcenter Flotherm 是一个功能强大且灵活的平台,支持如下功能:

• 兼容高级三维集成技术的详细芯片级热建模

• 带有真实边界条件的完整芯片—封装——系统热仿真

• 易于与标准 ASIC 设计流程集成

• 利用 EFFP 功能对非常复杂的设计进行精确建模

• 热感知三维分区和前期封装协同设计

• 复杂多芯片设计的 sign-off 热分析

• 跨芯片—封装设计流程的快速、详细、精确的热评估

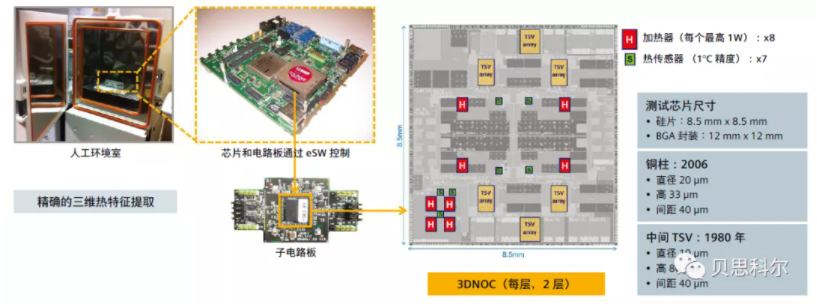

图 11:3DNOC - 热特征提取测试的实验设置(图片由 CEA-Leti 提供)。

CEA-Leti [参考文献 4、5] 描述了将集成 Sahara 项目的Simcenter Flotherm 用于 4G 电信应用的异构逻辑搭载逻辑三维片上网络异步多核器件,包括 DFT 和容错设计。

“ 所实现的热模型具有很高的精度,最坏情况下仿真数据和测量数据之差等于 3.75%,而考虑所有热传感器的平均差异低于 2%。” -- Pascal Vivet 博士,研究工程师,CEA-Leti

致谢

Byron Blackmore,Simcenter Flotherm 产品经理

Pascal Vivet,研究工程师,CEA-Leti

参考文献

1. Floorplan (microelectronics).

http://en.wikipedia.org/wiki/Floorplanning#Floorplanning

2. Physical design (electronics).

http://en.wikipedia.org/wiki/Physical_design_(electronics)

3. Simcenter provides design, verification, thermal and test solutions for TSMC’s CoWoS reference flow, Simcenter press pelease, October 15,2012.

http://www.mentor.com/company/news/mentor-tsmc-cowosreference-flow

4. Pascal Vivet, Yvain Thonnart, Romain Lemaire, Cristiano Santos, Edith Beigné, Christian Bernard, Florian Darve, Didier Lattard, Ivan Miro-Panadès, Denis Dutoit, Fabien Clermidy, S. Cheramy, Abbas Sheibanyrad, Frédéric Pétrot, Eric Flamand, Jean Michailos, Alexandre Arriordaz, Lee Wang, and Juergen Schloeffel (2017) “A 4× 4 × 2

homogeneous ccalable 3D network-on-chip circuit with 326 MFlit/s 0.66 pJ/b robust and fault tolerant asynchronous 3D links”, IEEE Journal of Solid State Circuits, Vol. 52 No. 1, pp.33-49.

5. Pascal Vivet. “Multi-scale thermal modeling methodology: application and exploration of 3D architectures”, Simcenter User Conference, April 2017, Santa Clara, CA.

更多业务咨询,请联系

电话:18998584819

邮箱:alin_li@basicae.com